Palminomicon

# **Palm OS Overview**

# **Terminology**

#### Hotsync

The act of synchronizing the data stored on the Palm with a backup stored on a PC. This can be done through the cradle or over a modem or infrared connection.

#### Cradle

Where the palm is docked for a hotsync.

#### Beaming

The act of transferring an object (binary file, database, database record, etc.) from one device to another over the IR port.

#### **Handspring Visor**

A less expensive Palm clone.

# **Development**

There are a suite of tools for Linux, including a GCC cross compiler.

Codewarrior released an IDE and emulator for Windows.

There is a Palm emulator called "POSE" that runs under Linux and Windows.

# Processor

All Palm OS machines run a clone of the 68000 processor running at 16MHz, called Dragonball (MC68328) on the Palms. There is also a more modern Dragonball EZ processor (MC68EZ328) in use in many models.

# **Display**

Screen resolution is 160x160.

In PalmOS 3.x and above, 4 shades of gray are supported, though most apps operate in monochrome mode.

(Some hacks hit 16 shades of gray using lots of inline assembly.)

The Palm IIIc is the only device in the family that shows color, and it is 8-bit indexed, 8-bits per channel.

# **Operating System**

Starting with the Palm III, the OS version is 3.0. This is the first version that supports grayscale and a variety of other features. It is also the lowest version we will support and the version we are building for.

In almost all cases, OS versions are backwards binary compatible. The API might change slightly from version to version.

Other PalmOS devices run various versions including 3.0, 3.0.2, 3.1, 3.2, 3.3, and 3.5.

Version 3.5 is required for color applications.

# **Memory Management**

Most devices come with 2MB, 4MB or 8MB of RAM/storage.

Each application running has access to the dynamic heap, which is quite small. Older devices have a 96K heap, while the newer ones have 128K.

The memory manager handles "chunks" of data which it is free to move around.

Chunks can be locked down for use by a program.

# **Databases**

Databases are a special form of memory chunks that are tagged with identifying information that can associate them with an application.

Databases can be thought of as memory mapped "files" which exist in RAM.

Sample usage: MemoPad.

Records can be added to and deleted from a database, and databases can be stored sorted.

Databases also have an area for application-specific information.

For ease, a file streaming interface has been implemented. Many apps continue to use the Database interface since it works well with their functionality.

Databases generally have the ".PDB" extension, but that varies according to specialized database types.

Databases can be prebuilt and

# **Applications**

Palm OS supports multiple tasks (processes) in theory, but not in practice.

The Launcher starts a new process for an Application, but the Application generally doesn't continue to run in the background when another Application is launched.

Each Application generally contains a "Form" which is a Window containing widget. (The application is free to create as many Windows as it wants, and they need not be Forms.)

The Application runs as an event-driven window system. Events are passed from the OS through a series of event handlers, some of which are within the application. The app can choose to handle certain events.

The executable is a ".PRC" file, which is itself a Database. It includes the binary code for the system as well as the resources used.

# Resource files

Resource files are specialized Databases that hold information about the UI widgets used in Forms and Windows, as well as other misc information about the Application (e.g. version number).

The resource file is defined as a text file (Unix) or using a GUI design tool (Codewarrior) and is compiled using a "resource compiler" into a format that can be included in the executable binary.

Widgets can be added and removed programatically at runtime, but it's generally a PITA compared to using the resource compiler.

# Communication

Serial communication is supported through the cradle, and over the IR port using a protocol called IRCOMM.

The Palm VII supports wireless internet connections.

Other devices support serial modem connections.

Some cradles use a USB connection for faster syncs, but the throughput is limited by the speed of the processor to somewhere under 4MB.

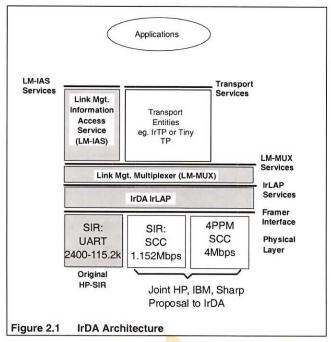

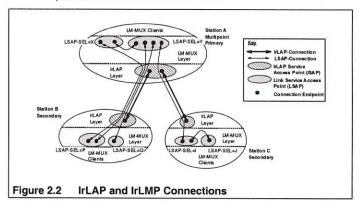

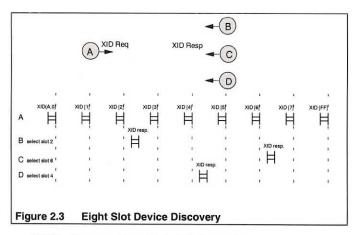

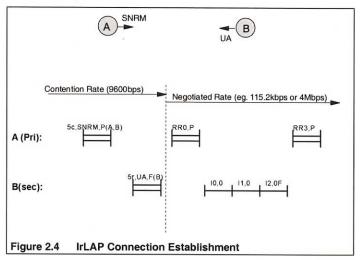

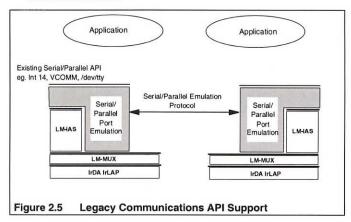

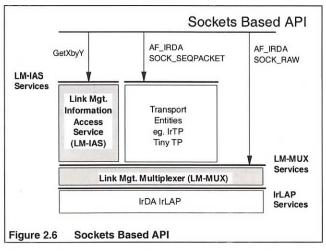

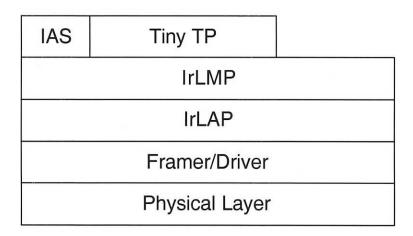

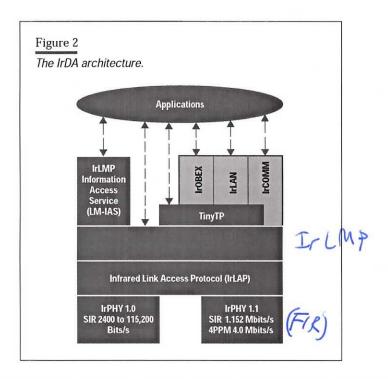

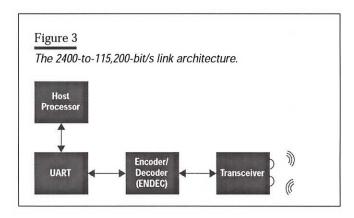

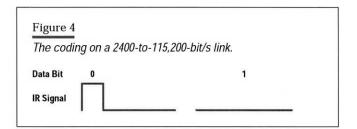

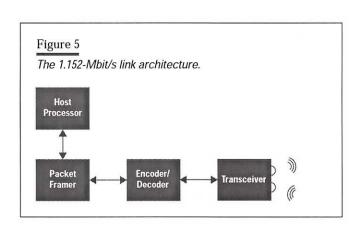

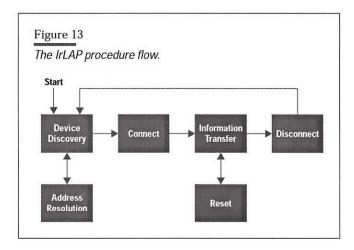

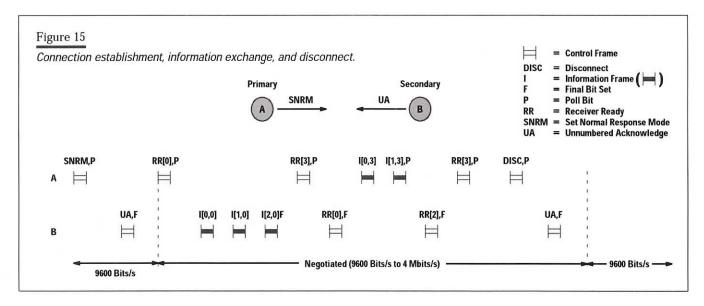

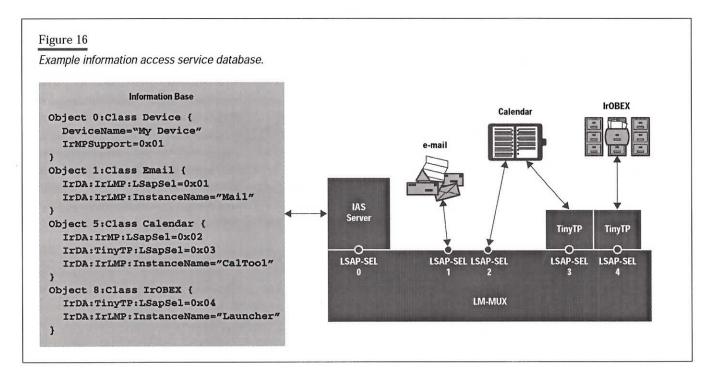

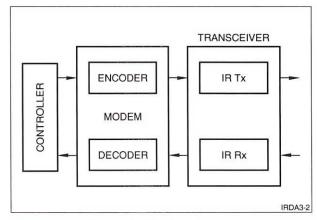

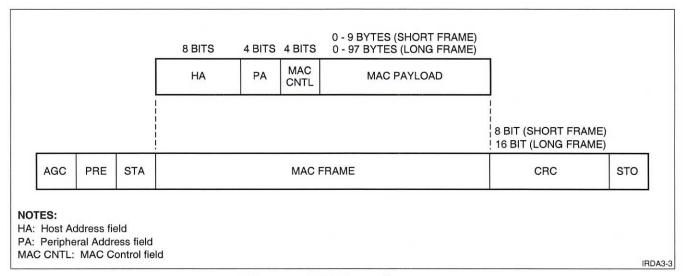

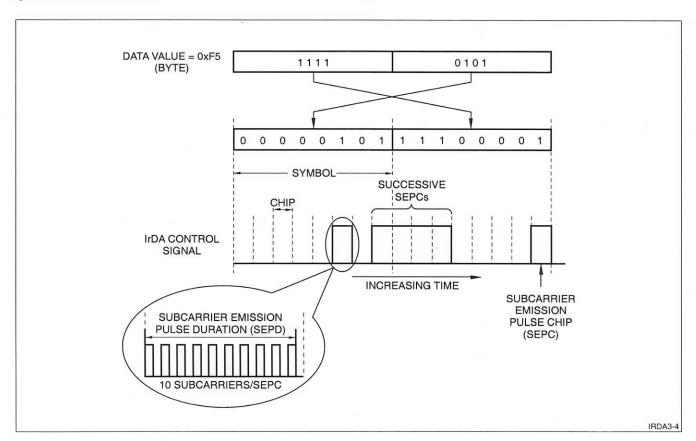

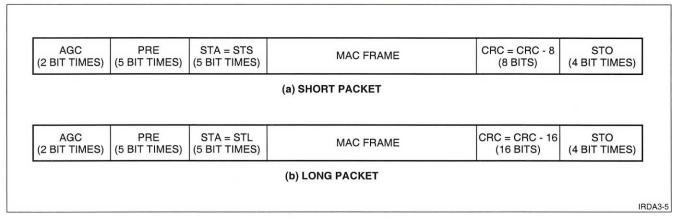

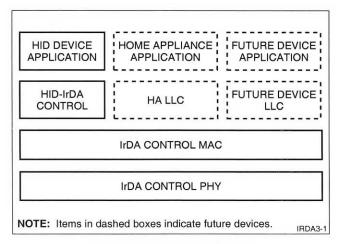

The IR port uses a common standard protocol called IrDA. It's a layered protocol where the upper layers correspond to high level protocols such as IRCOMM and IrOBEX.

IrOBEX is the protocol used when "beaming" data from one device to another.

The next layers down in the IR protocol stack can be accessed for complete control of the data transmitted (e.g. for a game.) (A homebuilt library for simplifying this complex process into a few function calls is being written.)

# **Drawing Primitives**

In Palm OSs before 3.5, there are black and white drawing primitives (line, rectangle, point, etc.) and hashed fill patterns.

Palm OS 3.5 introduces grayscale and color drawing primitives. (Which we can't use unless we also code support for older 3.0 models.)

Applications can create an offscreen window for drawing and double-buffering.

# **Bitmaps**

Bitmaps can be monochrome, grayscale, or color.

Bitmaps can be dynamically constructed at runtime using our homebuilt bitmap library.

Support for modification of bitmaps in versions before 3.5 is virtually nonexistant (except with our bitmap lib.)

Palm OS 3.5 introduces a method for using drawing primitives directly on a bitmap. (Which we can't use.)

# **Misc Hardware**

Some Palms, such as the IIIc and V, have built in rechargable batteries which power up while the device is docked in the cradle.

Linux (recent development kernels) supports IrDA, and we possess a cool IR dongle to experiment with transmitting from a PC to a palm.

The Visor has a plug-in slot for "Springboard Modules" ("Springboard" being the name of the tech used for the slot.) Examples of these cards are video games, memory expansion, cameras, MP3 players, GPSs (not yet available), etc.

# Resources

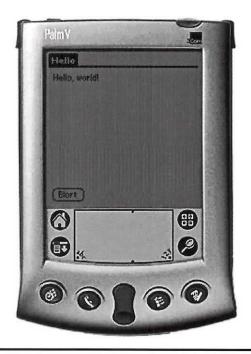

#### Hello.rcp:

```

#include "HelloRsc.h"

** Version number for application

VERSION ID 1000 "1.0"

** Description of main form

FORM ID HelloForm AT (0 0 160 160)

BEGIN

TITLE "Hello"

BUTTON "Blort" ID BlortButton AT (5 BOTTOM@156 AUTO AUTO)

END

** An alert message box

*/

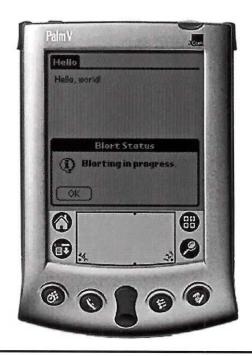

ALERT ID BlortAlert

INFORMATION

BEGIN

TITLE "Blort Status"

MESSAGE "Blorting in progress." BUTTONS "OK"

END

```

# Aug 08 b

#endif

return handled;

```

** Hello.c

#include <Pilot.h>

#include "HelloRsc.h"

#ifdef __GNUC_

#include "Callbacks.h"

#endif

** StartApplication()

static Err StartApplication (void)

// when the application starts, load its main form and jump to it

FrmGotoForm(HelloForm);

return 0;

** StopApplication()

static void StopApplication (void)

// any cleanup code goes here

** FormHandleEvent()

static Boolean FormHandleEvent(EventPtr event)

// handled is set true if no more processing on this event is required

Boolean handled = false;

#ifdef __GNUC_

CALLBACK_PROLOGUE

#endif

// what kind of event is it?

switch (event->eType) {

// the form is just opening, so init stuff and draw it

case frmOpenEvent:

FrmDrawForm(FrmGetActiveForm()); // display the form

WinDrawChars("Hello, world!", 13, 5, 20);

handled = true;

break;

// a button has been pressed

case ctlSelectEvent:

switch(event->data.ctlSelect.controlID) {

case BlortButton:

FrmAlert(BlortAlert); // pop up the alert box

handled = true;

break;

break;

#ifdef __GNUC_

CALLBACK EPILOGUE

```

## Hello.c

```

** ApplicationHandleEvent()

static Boolean ApplicationHandleEvent(EventPtr event)

FormPtr frm;

Int formId;

Boolean handled = false;

// this event happens when the form is first loaded and displayed

if (event->eType == frmLoadEvent) {

formId = event->data.frmLoad.formID;

frm = FrmInitForm(formId); // init

FrmSetActiveForm(frm); // activate

switch (formId) {

case HelloForm:

// set the event handler for this form

FrmSetEventHandler(frm, FormHandleEvent);

handled = true;

return handled;

** EventLoop()

static void EventLoop(void)

EventType event;

Word error;

do {

EvtGetEvent(&event, evtWaitForever);

if (!SysHandleEvent(&event)) {

if (!MenuHandleEvent(NULL, &event, &error)) {

if (!ApplicationHandleEvent(&event)) {

FrmDispatchEvent (&event);

} while (event.eType != appStopEvent);

** PilotMain()

DWord PilotMain (Word cmd, Ptr cmdPBP, Word launchFlags)

Err err = 0;

if (cmd == sysAppLaunchCmdNormalLaunch) {

if ((err = StartApplication()) == 0) {

EventLoop();

StopApplication();

}

return err;

```

HelloRsc.h

/\* pilrc generated file. Do not edit!\*/

#define BlortAlert 9997

#define BlortButton 9998

#define HelloForm 9999

```

Aug 08

14:39:43

```

## Callbacks.h

```

71

```

```

#ifndef __CALLBACK_H_

#define __CALLBACK_H_

/* This is a workaround for a bug in the current version of gcc:

gcc assumes that no one will touch %a4 after it is set up in crt0.o.

This isn't true if a function is called as a callback by something

that wasn't compiled by gcc (like FrmCloseAllForms()). It may also

not be true if it is used as a callback by something in a different

shared library.

We really want a function attribute "callback" which will insert this

progloue and epilogoue automatically.

- Ian */

register void *reg_a4 asm("%a4");

#define CALLBACK_PROLOGUE \

void *save_a4 = reg_a4; asm("move.1 %%a5,%%a4; sub.1 #edata,%%a4" : :);

#define CALLBACK_EPILOGUE reg_a4 = save_a4;

#endif

```

# Palm OS®

- Home Palm OS Platform Palm Economy Licensing **OEM Partnerships** Business Alliances > **Enterprise Getting Started** Technical Resources Business and Marketing > Solution Provider Program Platinum Program **News and Events** Provider Pavilion About Palm, Inc. Site Map Contacts

- Business Info Conduits Contact Palm Creator ID Dev Seeding

- Search 60 >

- Become a Developer!

- ▶ New Developers

Technologies

Tools

- ► Knowledge Base → Documentation → Support

#### **Hardware Comparison Matrix**

These are the currently released Palm OS® platform devices, including those from Palm Inc. licensees and OEMs. This list of the major differences between products is designed help developers understand product differences and product histories. This page is not intended to be a complete list of differences between products; minor differences in hardware and/or ROM revisions may also exist.

| Palm Inc. Products                        | Total RAM   | Dynamic Heap | Palm 08" Version | CPU Type | TCP Support | IR Support | Flashable ROM | ,                                                                                    |

|-------------------------------------------|-------------|--------------|------------------|----------|-------------|------------|---------------|--------------------------------------------------------------------------------------|

| Pilot 1000                                | 128K        | 32K          | 1.0              | DB       |             |            |               | No backlight.                                                                        |

| Pilot 5000                                | 512K        | 32K          | 1.0              | DB       |             |            |               | No backlight.                                                                        |

| Pilot w/1MB upgrade                       | 1MB         | 32K          | 1.0              | DB       |             |            |               | No backlight.                                                                        |

| PalmPilot[tm] Personal                    | 512K        | 32K          | 2.0              | DB       |             |            |               |                                                                                      |

| PalmPilot[tm] Pro                         | 1MB         | 64K          | 2.0              | DB       | x           |            |               |                                                                                      |

| PalmPilot[tm] Pro Upgrade                 | 1MB         | 64K          | 2.0              | DB       | x           |            |               | Upgrade for Pilot 1000, Pilot 5000, and PalmPilot Personal                           |

| Palm III[tm] organizer                    | 2MB         | 96K          | 3.0              | DB       | X           | x          | X             |                                                                                      |

| Palm[tm] 2MB upgrade                      | 2MB         | 96K          | 3.0              | DB       | X           | X          | х             | Upgrade for Pilot 1000, Pilot 5000, and PalmPilot Personal. Adds flash and IR.       |

| Palm IIIc[tm] organizer                   | 8MB         | 128K         | 3.5              | EZ       | X           | x          | х             | Rechargable lithium ion batteries. Color 160x160 screen.                             |

| Palm IIIx[tm] organizer                   | 4MB         | 128K         | 3.1              | EZ       | X           | x          | х             |                                                                                      |

| Palm IIIe[tm] organizer Special Edition   | 2MB         | 128K         | 3.3              | EZ       | X           | x          |               | French & German                                                                      |

| Palm IIIe[tm] organizer                   | 2MB         | 128K         | 3.3              | EZ       | X           | x          |               | Spanish                                                                              |

| Palm IIIe[tm] organizer & Special Edition | 2MB         | 128K         | 3.1              | EZ       | x           | x          |               |                                                                                      |

| Palm IIIxe[tm] organizer                  | 8MB         | 128K         | 3.5              | EZ       | X           | х          | X             | Rechargable lithium ion batteries                                                    |

| Palm V[tm] organizer                      | 2MB         | 128K         | 3.1              | EZ       | X           | X          | х             | Rechargable lithium ion batteries                                                    |

| Palm VII[tm] organizer                    | 2MB         | 128K         | 3.2              | DB§      | Х           | X          | X             | Built-in wireless connections.                                                       |

| Palm Vx[tm] organizer                     | 8MB         | 128K         | 3.3/3.5          | EZ       | X           | X          | X             | Rechargable lithium ion batteries. 2MB ROM                                           |

| Licensee and OEM Devices                  | 21.40       | 0717         | 2.00             | DD       |             |            |               | **************************************                                               |

| PageMart Synapse PagerCard                | 2MB         | 96K          | 3.0@             | DB       | X           |            |               | Includes alpha pager.                                                                |

| Symbol SPT1500                            | 2MB         | 96K          | 3.0.2¶           | DB       | X           | X          | Х             | Includes built-in scanner                                                            |

| Symbol SPT1700                            | 2 or        | 96K          | 3.2              | DB       | X           | X          | X             | Ruggedized device with                                                               |

|                                           | 8MB         |              |                  |          |             |            |               | built-in scanner.                                                                    |

| Symbol SPT1740                            | 2 or<br>8MB | 96K          | 3.2              | DB       | Х           | X          | Х             | Ruggedized device with<br>built-in scanner and Spectrum<br>24 wireless radio network |

interface.

| Handspring Visor            | 2 or<br>8MB | 128K | 3.1  | EZ | X | X |   | Springboard[tm] slot and built-in microphone.                                                                           |

|-----------------------------|-------------|------|------|----|---|---|---|-------------------------------------------------------------------------------------------------------------------------|

| IBM WorkPad PC Companion    | 2MB         | 96K  | 3.0  | DB | X | X |   | Original WorkPad PC<br>Companion                                                                                        |

| IBM WorkPad PC Companion    | 4MB         | 128K | 3.1  | EZ | X | X | X | English and Japanese versions.                                                                                          |

| IBM WorkPad c3 PC Companion | 2MB         | 128K | 3.1  | EZ | X | x |   | English and Japanese versions. Rechargable lithium ion batteries. Same form factor as Palm V[tm] organizer.             |

| Qualcomm pdQ smartphone     | 2MB         | 128K | 3.02 | DB | X | X |   | Built-in phone - pdQ 800 and pdQ 1900 differ only in carrier frequency a difference necessary based on the area of use. |

| TRG TRGpro                  | 8MB         | 128K | 3.3  | EZ | X | X | X | CompactFlash[tm] Type I/II slot. Improved audio.                                                                        |

CPU Types: If listed as "DB", it is the Motorola Dragonball NC68328 chip. If CPU is listed as "EZ", it is the Motorola Dragonball EZ chip, officially called the Motorola NC68EZ328.

§ Current Palm VII[tm] devices have the original Dragonball CPU. Future devices may use the Dragonball EZ CPU.

¶ Symbol SPT1500 ROM version should be 3.0.2r3. There may be devices with earlier ROM versions in the channel. Such units should update to ROM version 3.0.2 RELEASE 3 which fixes a potential data loss problem involving low-battery power management.

@ PagerCard does not add IR capability to the Palm Pilot 1000, 5000, Personal, or Pro models. However, it does not affect the existing IR capability of a Palm III[tm] device.

#### Hardware families

The following groups of devices use identical logic board designs, except for the memory card::

- 1. Pilot 1000, Pilot 5000, Pilot w/1MB upgrade

- 2. PalmPilot Personal, PalmPilot Professional.

- 3. Palm III[tm] organizer, Palm III[tm] Upgrade, original IBM WorkPad PC Companion

- 4. Palm V[tm] organizer, IBM Workpad c3 PC companion

# Palm OS<sup>®</sup>

Home

Palm OS Platform

Palm Economy

Licensing

OEM Partnerships

Business Alliances

Enterprise

Developers

Getting Started

Technical Resources

Business and Marketing

Solution Provider

Program

Platinum Program

News and Events

Provider Pavilion

About Palm, Inc. ►

Site Map ►

Contacts ►

Go

Quick Index

Business Info Conduits Contact Palm Creator ID Dev Seeding

Search G0 >

# ROM Image File Downloads (Clickwrap - USA Developers Only)

Each downloadable package contains a text file entitled "Appendix". Each such appendix shall be considered an appendix to your Prototype License and Confidentiality Agreement.

Palm OS® ROMs are intended for use with the Palm OS Emulator. For general information about the Emulator and links to documentation, tools, third-party extras, and other Emulator-related resources, see the Palm OS Emulator page. The newest versions of the Emulator are found on the Emulator Seeding page.

These images are not intended for reflashing ROMs in actual devices. This is **not supported.** If you do it anyway, make sure that the ROM image file matches the device. Doing this incorrectly can damage your device and/or your palm.net account. Since it is not supported, neither Palm customer support nor development support teams can facilitate nor help you recover from reflashing operations.

#### **About ROM Types**

For Palm OS software versions before 3.5, we provide individual ROM files for each device. Starting with Palm OS software version 3.5, we post platform ROMs for each ROM type. These are very nearly identical to shipping device ROMs for Palm OS 3.5 and greater and should be sufficient for any debugging purpose. However, if you wish to upload a ROM image from a device you posess, see the Emulator documentation for details.

EZ Devices with CPU MC68EZ328 Palm[tm] V, Vx, IIIx, and more.

non-EZ Devices with CPU MC68328 PalmPilot[tm], Palm[tm] III, and more.

Color Devices supporting color Palm[tm] IIIc, and more.

#### Palm VII[tm] ROMs

Palm VII[tm] ROM Images contain strong encryption technology and by United States law cannot be exported to certain countries. We can attempt to determine the country of origin of your Internet connection. If we determine that you are connecting from approved countries, you will be able to download the files. If we are unable to determine your country of connection (or you are connecting from an embargoed country), you will not be able to get these files from this web site.

Get Palm VII[tm] ROMs.

#### Palm OS® Software version 3.5

| Language | e ROM Type | Non-debug | Debug     |

|----------|------------|-----------|-----------|

| English  | Color      | Win / Mac | Win / Mac |

| English  | EZ         | Win / Mac | Win / Mac |

| English  | Non-EZ     | Win / Mac | Win / Mac |

| German   | Color      | Win / Mac | Win / Mac |

| German   | EZ         | Win / Mac | Win / Mac |

| German   | Non-EZ         | Win / Mac | Win / Mac |

|----------|----------------|-----------|-----------|

| Spanish  | Color          | Win / Mac | Win / Mac |

| Spanish  | EZ             | Win / Mac | Win / Mac |

| Spanish  | Non-EZ         | Win / Mac | Win / Mac |

| French   | Color          | Win / Mac | Win / Mac |

| French   | EZ             | Win / Mac | Win / Mac |

| French   | Non-EZ         | Win / Mac | Win / Mac |

| Italian  | Color          | Win / Mac |           |

| Italian  | EZ             | Win / Mac |           |

| Italian  | Non-EZ         | Win / Mac |           |

| Japanese | Color          | Win / Mac |           |

| Japanese | EZ             | Win / Mac |           |

| Japanese | EZ - 2MB flash | Win / Mac |           |

|          |                |           |           |

There are also pre-release versions of Palm OS software version 3.5 with web clipping wireless support. ROM images with web clipping contain strong encryption technology and by United States law cannot be exported to certain countries. We can attempt to determine the country of origin of your Internet connection. If we determine that you are connecting from approved countries, you will be able to download the files. If we are unable to determine your country of connection (or you are connecting from an embargoed country), you will not be able to get these files from this web site. Get Web Clipping ROMs.

#### Palm OS® Software version 3.3

| Language | e ROM Type                                          | Non-debug | Debug     |

|----------|-----------------------------------------------------|-----------|-----------|

| English  | Palm III[tm] organizer                              | Win / Mac | Win / Mac |

| English  | Palm V[tm], Palm Vx[tm], & Palm IIIx[tm] organizers | Win / Mac | Win / Mac |

| French   | Palm III[tm] organizer                              | Win / Mac |           |

| French   | Palm V[tm], Palm Vx[tm], & Palm IIIx[tm] organizers | Win / Mac |           |

| German   | Palm III[tm] organizer                              | Win / Mac |           |

| German   | Palm V[tm], Palm Vx[tm], & Palm IIIx[tm] organizers | Win / Mac |           |

#### Palm OS® Software version 3.2

Palm VII[tm] ROM images contain strong encryption technology and by United States law cannot be exported to certain countries. We can attempt to determine the country of origin of your Internet connection. If we determine that you are connecting from approved countries, you will be able to download the files. If we are unable to determine your country of connection (or you are connecting from an embargoed country), you will not be able to get these files from this web site.

Get Palm VII[tm] ROMs.

# Palm OS® Software version 3.1

| Language | e ROM Type                               | Non-debug | Debug     |

|----------|------------------------------------------|-----------|-----------|

| English  | Palm V[tm] organizer                     | Win / Mac | Win / Mac |

| English  | Palm IIIx[tm] & Palm IIIe[tm] organizers | Win / Mac | Win / Mac |

| French   | Palm V & Palm IIIx organizers            | Win / Mac |           |

| German   | Palm V & Palm IIIx organizers            | Win / Mac |           |

| Spanish  | Palm V & Palm IIIx organizers            | Win / Mac |           |

#### Palm OS® Software version 3.0

| Language ROM Type |                        | Non-debug | Debug     |

|-------------------|------------------------|-----------|-----------|

| English           | Palm III[tm] organizer | Win / Mac | Win / Mac |

| French            | Palm III organizer     | Win / Mac |           |

| German            | Palm III organizer     | Win / Mac |           |

| Spanish           | Palm III organizer     | Win / Mac |           |

## Palm OS® software version 2.0

| Languag | e ROM Type                           | Non-debug | Debug     |

|---------|--------------------------------------|-----------|-----------|

| English | PalmPilot Professional[tm] organizer | Win / Mac | Win / Mac |

| English | PalmPilot Personal[tm] organizer     | Win / Mac |           |

## Palm OS® software version 1.0

| Languag | e ROM Type                                 | Non-debug |

|---------|--------------------------------------------|-----------|

| English | Pilot 1000[tm] & Pilot 5000[tm] organizers | Win / Mac |

**SEARCH**

#### MC68328: DragonBall[tm] Integrated Microprocessor

**Page Contents**

Documentation

Design Tools

Questions

Frequently Asked

**Parametrics**

Features

Tools

#### **ADVANCED**

| T .    | P   | ~ .  |    |

|--------|-----|------|----|

| Prod   | mot | Cata | 00 |

| 1 1 UU | uct | Cala | w  |

Microprocessors

32 Bit

68K/ColdFire

M683XX

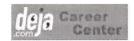

As the portable consumer market grows at full speed, system requirements are becoming more rigorous than ever. Minimum components, small board space, low power consumption, and low system cost are several minimum criteria to a successful product. To address these needs, Motorola designed the MC68328 DragonBall[tm] processor. By providing 3.3V, fully static operation in an efficient package, the MC68328

static operation in an efficient package, the MC68328 delivers cost-effective performance to satisfy the extensive requirements of today's portable consumer market.

Product Picture

#### \_\_\_\_\_

#### **Related Links**

#### General DragonBall Information

#### MC68328 Features

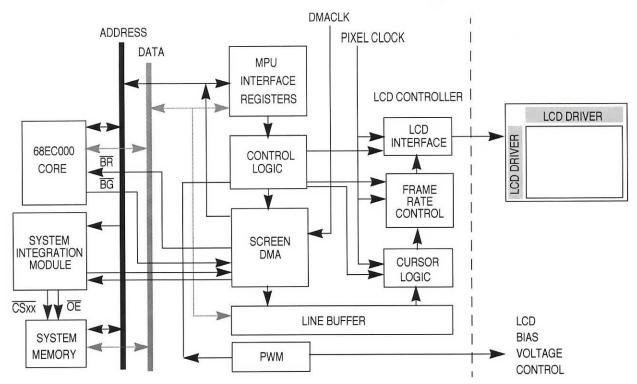

- Static 68EC000 Core Processor-Identical to MC68EC000 Microprocessor

- O Full Compatibility With MC68000 And MC68EC000

- 32-Bit both External and Internal Address Bus capable of addressing 4GB Space

- O 16-Bit On-Chip Data Bus For MC68000 Bus Operations

- Static Design Allows Processor Clock To Be Stopped Providing Dramatic Power Savings

- O 2.7 MIPS Performance At 16.67-MHz Processor Clock

- External M68000 Bus Interface with Dynamic Bus Sizing for 8-bit and 16-bit Data Ports

- System Integration Module (SIM28), Incorporating Many Functions Typically Relegated to External Array Logic, such as:

- O System Configuration, Programmable Address Mapping

- O Glueless Interface to SRAM, EPROM, FLASH Memory

- O Sixteen Programmable Peripheral Chip Selects With Wait State Generation Logic

- O Interrupt Controller with 13 flexible inputs

- Programmable Interrupt Vector Response For On-Chip Peripheral Modules

- O Hardware Watchdog Timer

- O Software Watchdog Timer

- O Low-Power Mode Control

- O Up to 78-Bit Individually Programmable Parallel I/O Ports

- O PCMCIA 1.0 Support

- UART

- O Support IrDA Physical Layer Protocol

- O 8 Bytes FIFO on Rx and Tx

- Two Separated Serial Peripheral Interface Ports (Master and Slave)

- O Support For External POCSAG Decoder (Slave)

- O Support for Digitizer from A/D Input or EEPROM (Master)

- Dual Channel 16-Bit General Purpose Counter/timer

- O Multimode Operation, Independent Capture/Compare Registers

- O Automatic Interrupt Generation

- O 240-ns Resolution At 16.67-MHz System Clock

- O Each Timer Has An Input And An Output Pin for Capture and Compare

- Pulse Width Modulation Output For Sound Generation

- O Programmable Frame rate

- O 16 Bit programmable

- O Supports Motor Control

- Real Time Clock

- O 24 Hour Time

- One Programmable Alarm

- Power Management

- O 5 V or 3.3 V Operation

- O Fully Static HCMOS Technology

- O Programmable Clock Synthesizer for Full Frequency Control

- O Low Power Stop Capabilities

- O Modules Can Be Individually Shut-down

- O Lowest Power Mode Control (Shut Down CPU and Peripherals)

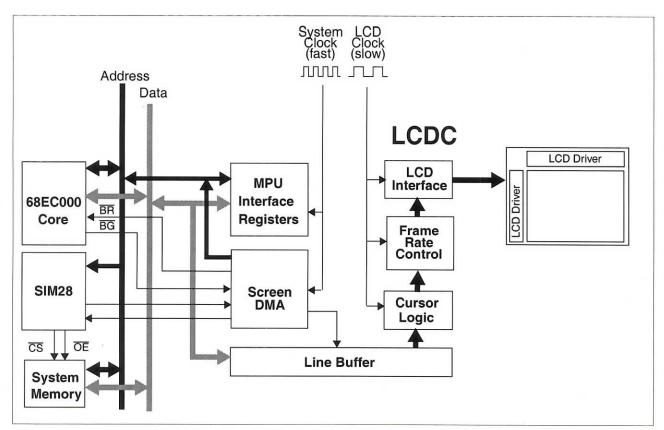

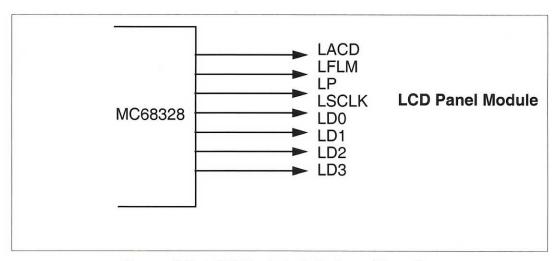

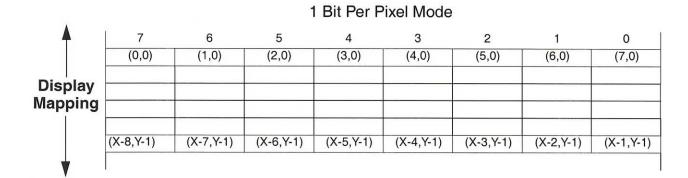

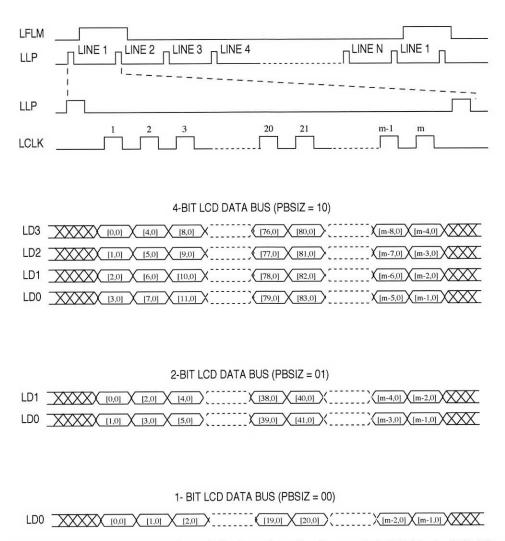

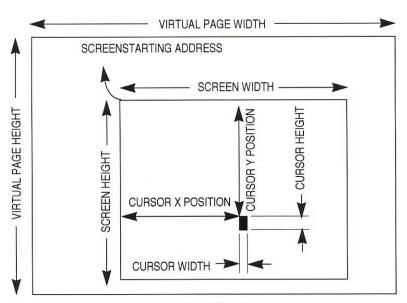

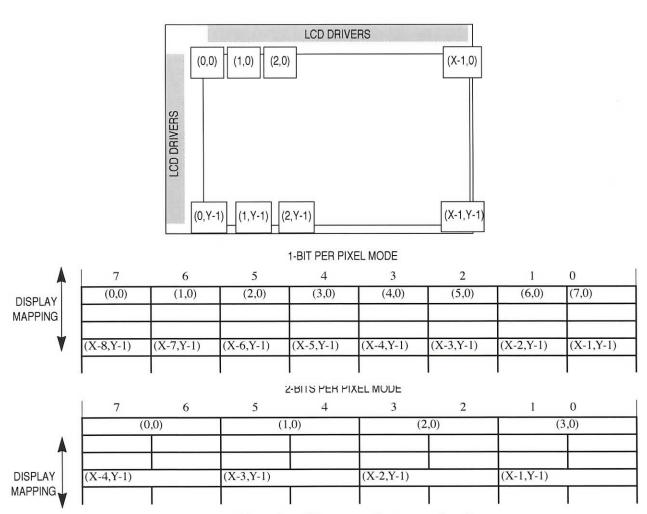

- LCD Control Module

- Software Programmable Screen Size To Support Single (Non-Split) Monochrome/ STN Panels

- O Capable Of Direct Driving Popular LCD Drivers/Modules From Motorola, Sharp, Hitachi, Toshiba etc.

- O Support Up To 4 Grey Levels

- O Utilize System Memory as Display Memory

- IEEE 1149.1 Boundary Scan Test Access Port (JTAG)

- Operation From DC To 16.67 MHz (Processor Clock)

- Operating Voltages of  $3.3V \pm 0.3V$  and  $5V \pm 0.5V$

- Compact 144-Lead Thin Quad Flat Pack (TQFP) Package

[top]

#### MC68328 Parametrics

| Processor Speed<br>(MHz) | Bus Interface<br>(Bits) | Performance_1<br>(MIPS) | Voltage<br>(V) | Package  |

|--------------------------|-------------------------|-------------------------|----------------|----------|

| 16                       | 32 addr/16 data         | 2.7 @ 16MHz             | 3.3 - 5.0      | 144 TQFP |

[top]

#### MC68328 Documentation

#### **Application Note**

| Document ID      | Name                                                                    | Type                | Format | Size | Rev | Date Last<br>Modified |

|------------------|-------------------------------------------------------------------------|---------------------|--------|------|-----|-----------------------|

| MC68EZ328DLFLASH | MC68EZ328 Methods of<br>downloading code or data to<br>flash            | Application<br>Note | pdf    | 30k  | 1   | 14-DEC-1996           |

| MC68EZ328DTMF    | Generating DTMF with PWM module                                         | Application<br>Note | pdf    | 241k | 1   | 15-FEB-1999           |

| MC68EZ328KEYPAD  | MC68EZ328 Minimum I/O<br>to Matrix Keyboard with<br>DragonBall TM EZ328 | Application<br>Note | pdf    | 89k  | 1   | 30-SEP-1998           |

| MC68EZ328PLLVCC  | PLLVCC Circuit Design for                                               | Application         | pdf    | 38k  | 1   | 17-SEP-1998           |

|                 | DragonBall TM (MC68328)<br>and DragonBall TM -EZ<br>(MC68EZ328) | Note                |     |     |   |             |

|-----------------|-----------------------------------------------------------------|---------------------|-----|-----|---|-------------|

| MC68EZ328PWM    | MC68EZ328 Audio<br>Generation by DragonBall<br>TM MC68EZ328     | Application<br>Note | pdf | 79k | 1 | 06-NOV-1998 |

| MC68EZ328SRAM16 | MC68EZ328 16bit SRAM<br>Interface                               | Application<br>Note | pdf | 70k | 1 | 12-NOV-1998 |

| AN1767/D        | MC68328 and MC68EZ328<br>DragonBall Power<br>Management         | Application<br>Note | pdf | 26k | 0 | 30-SEP-1998 |

| Fact | Sheets |

|------|--------|

|      |        |

Document IDNameTypeFormatSizeRevDate Last ModifiedM68000MTSMemory Test Software for 68KFact Sheetspdf114k001-JAN-1999

| Miscellaneous    |                                                                              |               |        |      |     |                       |

|------------------|------------------------------------------------------------------------------|---------------|--------|------|-----|-----------------------|

| Document ID      | Name                                                                         | Type          | Format | Size | Rev | Date Last<br>Modified |

| MC68328P/D       | MC68328 and MC68328V<br>Integrated Portable System<br>Processor - DragonBall | Miscellaneous | pdf    | 26k  | 1   | 05-OCT-1995           |

| XC68328PV        | MC68328 Chip Errata -<br>Mask 3G58E/OH51K                                    | Miscellaneous | pdf    | 10k  | 1.0 | 18-JUL-1996           |

| MC68EZ328CC      | Contrast Circuit for Postive VEE                                             | Miscellaneous | pdf    | 7k   | 0   | 04-NOV-1998           |

| MC68EZ328LPF     | EZ328 Demo                                                                   | Miscellaneous | pdf    | 16k  | 2   | 19-APR-1998           |

| MC68EZ328PCMCIA2 | MC68EZ328 PCMCIA<br>Release 2.0 Interface Board<br>for DragonBall Update     | Miscellaneous | pdf    | 180k | 1   | 26-NOV-1998           |

| Reference Man      | ual                                    |                     |        |      |     |                       |

|--------------------|----------------------------------------|---------------------|--------|------|-----|-----------------------|

| <b>Document ID</b> | Name                                   | Type                | Format | Size | Rev | Date Last<br>Modified |

| M68000PM/ER        | 68K Programmer's Ref.<br>Manual Errata | Reference<br>Manual | txt    | 0k   | •   | -                     |

| Users Guide   |                                                                      |                |        |      |     |                       |

|---------------|----------------------------------------------------------------------|----------------|--------|------|-----|-----------------------|

| Document ID   | Name                                                                 | Туре           | Format | Size | Rev | Date Last<br>Modified |

| MC68328UM/D   | MC68328 DragonBall<br>Microprocessor User's Manual<br>Preliminary    | Users<br>Guide | pdf    | 547k | 1   | 06-NOV-1997           |

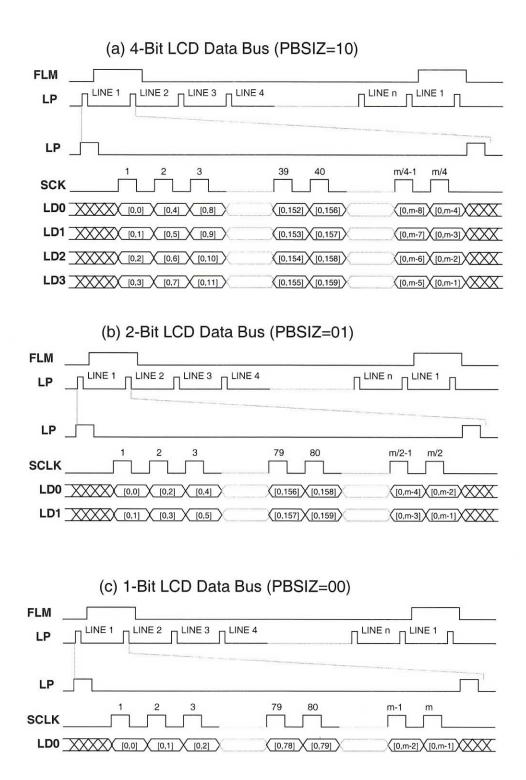

| MC68328UMA1/D | MC68328 User's Manual<br>Addendum - LCD Controller<br>Timing Diagram | Users<br>Guide | pdf    | 17k  | 0   | 23-OCT-1998           |

| MC68328UMA2/D | MC68328 User's Manual<br>Addendum - ID Register                      | Users<br>Guide | pdf    | 86k  | 0   | 14-JAN-1999           |

| MC68328UME/D  | MC68328 Spec Errata for<br>DragonBall MC68EZ328 User's<br>Manual     | Users<br>Guide | pdf    | 18k  | 0   | 01-NOV-1997           |

| MC68000UM/D   | M68000 8-16-32-Bit<br>Microprocessors User's Manual                  | Users<br>Guide | pdf    | 998k | 9   | 31-DEC-1993           |

Addendum

Guide

pdf 37k 1 31-DEC-1994

[top]

#### MC68328 Tools

#### Tools

| 10015         |                                                                 |                                 |        |      |     |                       |

|---------------|-----------------------------------------------------------------|---------------------------------|--------|------|-----|-----------------------|

| Document ID   | Name                                                            | Type                            | Format | Size | Rev | Date Last<br>Modified |

| M68000SC1     | Ackerman Benchmark With a<br>Downloadable C Source Code<br>File |                                 | txt    | 0k   | -   | 20-DEC-1993           |

| M68000SC6     | Dhrystone 2.1 Benchmarking<br>Part 1 (C Header File)            | Dhrystones                      | txt    | 17k  | 2.1 | 25-MAY-1988           |

| M68000SC7     | Fibonacci Benchmark With<br>Downloadable C Source Code<br>File  |                                 | txt    | 1k   | 8   | 20-DEC-1993           |

| M68000SC8     | Sieve Benchmark With<br>Downloadable C Source Code<br>File      |                                 | txt    | 1k   | •   | 20-DEC-1993           |

| M68000SC9     | Dhrystone 2.1 Benchmarking<br>Part 1                            | Dhrystones                      | txt    | 6k   | 2.1 | 25-MAY-1988           |

| M68000BFP     | S-Record to C-Struct or Binary<br>File Program                  | Software<br>Developers<br>Tools | txt    | 7k   | •   | -                     |

| M68000ASS/SIM | 68000 Assembler/Simulator for MS-DOS                            | Software<br>Developers<br>Tools | zip    | 156k | 27  | -                     |

| M68000XASS    | M680x0 cross assembler<br>MS-DOS                                | Software<br>Developers<br>Tools | zip    | 113k | -   | ~                     |

| M68000UNIX    | 68K Assembler-Berkeley UNIX                                     | Software<br>Developers<br>Tools | arc    | 67k  | •   | -                     |

| M68000AS332   | AS332.ARC-Freeware                                              | Software<br>Developers<br>Tools | arc    | 57k  | -   | 1.00                  |

| M68000ASMBLR  | 68K Assembler v 2.71                                            | Software<br>Developers<br>Tools | lzh    | 54k  | 7   |                       |

| M68000CPLR    | 68K Compiler                                                    | Software<br>Developers<br>Tools | html   | 0k   |     |                       |

| M68000MON     | Monitor for 68K Educational<br>Computer Board                   | Software<br>Developers<br>Tools | zip    | 148k |     | -                     |

| M68000AMPRT   | Amiga Port of Matthew<br>Brandt's CC68K Compiler                | Software<br>Developers<br>Tools | html   | 0k   | -   |                       |

[top]

#### MC68328 Design Tools and Data

ID

Name

MC68328ADS

MC68328 Application Development System

MC68328ADSUM/D

MC68328 Application Development System User's

# Manual MC68328SCHEMATICS MC68328 User's manual ORCAD[tm] Schematics

[top]

Home | Solutions | Products | Support | Contact | About Us | Site Map |

Motorola Semiconductor Products

Copyright Info Privacy Terms

SEARCH

#### MC68EZ328: DragonBall EZ Integrated Processor

#### **ADVANCED**

**Product Catalog**

The MC68EZ328 is the second member of the

DragonBall[tm] Series of Integrated Portable System

Microprocessors Processors.

32 Bit

Inheriting the display capability of the original DragonBall processor, the MC68EZ328 features a more flexible LCD controller with streamlined list of peripherals placed in a smaller package. This processor mainly targeted for portable consumer products which

68K/ColdFire

M683XX

mainly targeted for portable consumer products which require less peripherals and a more flexible LCD controller. By providing 3V, fully static operation in an efficient 100 TQFP package, the MC68EZ328 delivers cost-effective performance to satisfy the extensive requirements of today's portable consumer market.

#### **Page Contents**

- Features

- Parametrics

- Documentation

- Tools

- Design Tools

- Frequently Asked Questions

#### **Related Links**

General DragonBall Information

#### MC68EZ328 Features

- Static 68EC000 Core Processor-Identical to MC68EC000 Microprocessor

- O Full Compatibility with MC68000 and MC68EC000

- O 32-Bit internal address bus

- O 24-Bit external address bus capable of addressing maximum 4 x 16MB blocks with chip selects CSA, CSB and 4 x 4 MB blocks with chip selects CSC, CSD:

- O 16-Bit on-chip data bus for MC68000 bus operations

- Static design allows processor clock to be stopped to provide power savings

- O 2.7 MIPS Performance at 16.58 MHz processor clock

- O External M68000 Bus interface with selectable bus sizing for 8-bit and 16-bit data ports

- System Integration Module (SIM28-EZ), Incorporating Many Functions Typically Related to External Array Logic, such as:

- O System configuration, programmable address mapping

- O Glueless interface to SRAM, EPROM, FLASH memory

- O 8 programmable chip selects with wait state generation logic

- O 4 programmable interrupt I/O and with keyboard interrupt capability

- O 5 general purpose, programmable edge/level/polarity interrupt IRQ

- O Other programmable I/O, multiplexed with peripheral functions up to 47 parallel I/O

- O Programmable interrupt vector response for on-chip peripheral modules

- O Low-Power mode control

- DRAM Controller

- O Support CAS-before-RAS refresh cycles and self-refresh mode DRAM

- O Support 8 bit / 16 bit port DRAM

- O EDO or Automatic Fast Page Mode for LCDC access

- O Programmable refresh rate

- O Support up to 2 banks of DRAM/EDO DRAM

- O Programmable column address size

- UART

- O Support IrDA physical layer protocol up to 115.2kbps

- O 8 Bytes FIFO on Tx and 12 Bytes FIFO on Rx

- Serial Peripheral Interface Port

- O 16 bit programmable SPI to support external peripherals

- O Master mode support

- 16-Bit General Purpose Counter / Timer

- O Automatic interrupt generation

- O 60-ns resolution at 16.58-MHz system clock

- O Timer Input/Output pin

- Real Time Clock / Sampling Timer

- O Separate power supply for the RTC

- One programmable alarm

- O Capable to count up to 512 days

- O Sampling Timer with selectable frequency (4Hz, 8Hz, 16Hz, 32Hz, 64Hz, 256Hz, 512Hz, 1kHz). Generate interrupt for digitizer sampling, or keyboard debouncing.

- LCD Controller

- O Software programmable screen size (up to 640\*512) to support single (Non-Split) monochrome/ color STN panels

- Capable of direct driving popular LCD drivers/modules from Motorola, Sharp, Hitachi, Toshiba etc.

- O Support up to 4 grey levels out of 16 palettes.

- O Utilize system memory as display memory

- O LCD contrast control using 8-bit PWM

- Pulse Width Modulation (PWM) Module

- O 8 bit resolution

- O 5 Byte FIFO provide more flexibility on performance

- O Sound and melody generation

- Build-in Emulation Function

- O Dedicated memory space for Emulator Debug Monitor with Chip Select

- O Dedicated interrupt (Interrupt Level 7) for ICE

- One address signal comparator and one control signal comparator with masking to support single or multiple Hardware Execution Breakpoint

- One breakpoint instruction insertion unit

- Boot Strap Mode Function

- Allow User to initialize system and download program/data to system memory through UART

- O Accept execution command to run program stored in system memory

- Provide an 8-byte long Instruction Buffer for 68000 instruction storage and execution

- Power Management

- O Fully static HCMOS technology

- Programmable clock synthesizer using 32.768 kHz/38.4 kHz crystal for full frequency control

- O Low power stop capabilities

- O Modules can be individually shut-down

- O Lowest power mode control

- Operation from DC To 16.58 MHz (processor clock)

- Operating Voltage of 3.0 V to 3.6 V

- Compact 100-Lead Thin Quad Flat Pack (TQFP) and 144 Pin Ball Grid Array (PBGA) packages

## MC68EZ328 Parametrics

| <b>Processor Speed</b> | <b>Bus Interface</b> | Performance_1 | Voltage   |          |

|------------------------|----------------------|---------------|-----------|----------|

| (MHz)                  | (Bits)               | (MIPS)        | (V)       | Package  |

| 20                     | 24 addr/16 data      | 3.4 @ 20 MHz  | 3.0 - 3.6 | 100 TQFP |

[top]

## MC68EZ328 Documentation

| App | lica | tion | Not | e |

|-----|------|------|-----|---|

|-----|------|------|-----|---|

| <b>Document ID</b> | Name                                                                                         | Туре                | Format | Size | Rev | Date Last<br>Modified |

|--------------------|----------------------------------------------------------------------------------------------|---------------------|--------|------|-----|-----------------------|

| AN1767/D           | MC68328 and MC68EZ328<br>DragonBall Power<br>Management                                      | Application<br>Note | pdf    | 26k  | 0   | 30-SEP-1998           |

| MC68EZ328DLFLASH   | MC68EZ328 Methods of downloading code or data to flash                                       | Application<br>Note | pdf    | 30k  | 1   | 14-DEC-1996           |

| MC68EZ328DTMF      | Generating DTMF with PWM module                                                              | Application<br>Note | pdf    | 241k | 1   | 15-FEB-1999           |

| MC68EZ328KEYPAD    | MC68EZ328 Minimum I/O<br>to Matrix Keyboard with<br>DragonBall TM EZ328                      | Application<br>Note | pdf    | 89k  | 1   | 30-SEP-1998           |

| MC68EZ328PWM       | MC68EZ328 Audio<br>Generation by DragonBall<br>TM MC68EZ328                                  | Application<br>Note | pdf    | 79k  | 1   | 06-NOV-1998           |

| MC68EZ328SRAM16    | MC68EZ328 16bit SRAM<br>Interface                                                            | Application<br>Note | pdf    | 70k  | 1   | 12-NOV-1998           |

| MC68EZ328PLLVCC    | PLLVCC Circuit Design for<br>DragonBall TM (MC68328)<br>and DragonBall TM -EZ<br>(MC68EZ328) | Application<br>Note | pdf    | 38k  | 1   | 17-SEP-1998           |

|  | Fact | Sheets |

|--|------|--------|

|--|------|--------|

| Document ID Name                       | Type        | Format | Size | Rev | Date Last Modified |

|----------------------------------------|-------------|--------|------|-----|--------------------|

| M68000MTS Memory Test Software for 68K | Fact Sheets | pdf    | 114k | 0   | 01-JAN-1999        |

| Miscellaneous    |                                                                                     |               |        |      |     |                       |

|------------------|-------------------------------------------------------------------------------------|---------------|--------|------|-----|-----------------------|

| Document ID      | Name                                                                                | Type          | Format | Size | Rev | Date Last<br>Modified |

| MC68EZ328/H      | MC68EZ328 DragonBall<br>EZ Integrated Portable<br>System Processor Product<br>Brief | Miscellaneous | pdf    | 152k | 1.3 | 01-JAN-1998           |

| MC68EZ328CE1J75C | MC68EZ328 -<br>DragonBall-EZ Masket<br>1J75C                                        | Miscellaneous | pdf    | 18k  | 0.1 | 24-MAR-1998           |

| MC68EZ328CE1J83G | MC68EZ328 -<br>DragonBall-EZ Masket<br>1J83G                                        | Miscellaneous | pdf    | 15k  | 0.1 | 20-JAN-1999           |

| MC68EZ328PCMCIA2 | MC68EZ328 PCMCIA<br>Release 2.0 Interface Board<br>for DragonBall Update            | Miscellaneous | pdf    | 180k | 1   | 26-NOV-1998           |

| MC68EZ328CC      | Contrast Circuit for Postive VEE                                                    | Miscellaneous | pdf    | 7k   | 0   | 04-NOV-1998           |

| Reference Manual |                                        |                     |        |      |     |                       |  |

|------------------|----------------------------------------|---------------------|--------|------|-----|-----------------------|--|

| Document ID      | Name                                   | Туре                | Format | Size | Rev | Date Last<br>Modified |  |

| M68000PM/ER      | 68K Programmer's Ref.<br>Manual Errata | Reference<br>Manual | txt    | 0k   | •   | -                     |  |

#### **Selector Guide**

| Document ID | Name                                                                              | Type              | Format | Size | Rev | Date Last Modified |

|-------------|-----------------------------------------------------------------------------------|-------------------|--------|------|-----|--------------------|

| SG167/D     | 68K/Coldfire Product Selector<br>Guide: Networking Systems Division<br>2nd Q 1999 | Selector<br>Guide | pdf    | 444k | 27  | 31-MAR-1999        |

| Users Guide    |                                                     |                |        |       |     |                       |  |  |  |

|----------------|-----------------------------------------------------|----------------|--------|-------|-----|-----------------------|--|--|--|

| Document ID    | Name                                                | Type           | Format | Size  | Rev | Date Last<br>Modified |  |  |  |

| MC68EZ328UM/D  | MC68EZ328 Users Manual -<br>DragonBall-EZ(tm)       | Users<br>Guide | pdf    | 2488k | 1   | 01-NOV-1998           |  |  |  |

| MC68EZ328UMA/D | MC68EZ328 Users Manual<br>Addendum                  | Users<br>Guide | pdf    | 16k   | 1   | 12-JAN-1999           |  |  |  |

| MC68000UM/D    | M68000 8-16-32-Bit<br>Microprocessors User's Manual | Users<br>Guide | pdf    | 998k  | 9   | 31-DEC-1993           |  |  |  |

[top]

#### MC68EZ328 Tools

#### Tools

| 0015          |                                                                 |                                 |        |      |              |                       |

|---------------|-----------------------------------------------------------------|---------------------------------|--------|------|--------------|-----------------------|

| Document ID   | Name                                                            | Type                            | Format | Size | Rev          | Date Last<br>Modified |

| M68000SC1     | Ackerman Benchmark With a<br>Downloadable C Source Code<br>File |                                 | txt    | 0k   | -            | 20-DEC-1993           |

| M68000SC6     | Dhrystone 2.1 Benchmarking<br>Part 1 (C Header File)            | Dhrystones                      | txt    | 17k  | 2.1          | 25-MAY-1988           |

| M68000SC7     | Fibonacci Benchmark With<br>Downloadable C Source Code<br>File  |                                 | txt    | 1k   | -            | 20-DEC-1993           |

| M68000SC8     | Sieve Benchmark With<br>Downloadable C Source Code<br>File      |                                 | txt    | 1k   | 21           | 20-DEC-1993           |

| M68000CPLR    | 68K Compiler                                                    | Software<br>Developers<br>Tools | html   | 0k   | ٠            | .=                    |

| M68000ASS/SIM | 68000 Assembler/Simulator for MS-DOS                            | Software<br>Developers<br>Tools | zip    | 156k | <del>-</del> | -                     |

| M68000AS332   | AS332.ARC-Freeware                                              | Software<br>Developers<br>Tools | arc    | 57k  | •            | .5.                   |

| M68000UNIX    | 68K Assembler-Berkeley UNIX                                     | Software<br>Developers          | arc    | 67k  | -            | -                     |

|              |                                                  | Tools                           |      |      |     |             |

|--------------|--------------------------------------------------|---------------------------------|------|------|-----|-------------|

| M68000XASS   | M680x0 cross assembler<br>MS-DOS                 | Software<br>Developers<br>Tools | zip  | 113k | -   |             |

| M68000MON    | Monitor for 68K Educational<br>Computer Board    | Software<br>Developers<br>Tools | zip  | 148k | -   | -           |

| M68000ASMBLR | 68K Assembler v 2.71                             | Software<br>Developers<br>Tools | lzh  | 54k  | -   | -           |

| M68000AMPRT  | Amiga Port of Matthew<br>Brandt's CC68K Compiler | Software<br>Developers<br>Tools | html | 0k   |     |             |

| M68000BFP    | S-Record to C-Struct or Binary<br>File Program   | Software<br>Developers<br>Tools | txt  | 7k   | -   | 1-          |

| M68000SC9    | Dhrystone 2.1 Benchmarking<br>Part 1             | Dhrystones                      | txt  | 6k   | 2.1 | 25-MAY-1988 |

[top]

#### MC68EZ328 Design Tools and Data

ID

Name

MC68EZ328ADS

MC68EZ328 Application Development System

[top]

$Home \mid Solutions \mid Products \mid Support \mid Contact \mid About \; Us \mid Site \; Map \mid$

Motorola Semiconductor Products

Copyright Info Privacy Terms

< Home < Developers < Development Support < Knowledge Base

# **Developer Knowledge Base**

# Palm OS®

Home

Palm OS Platform

Palm Economy

Enterprise

Licensing

DEM Partnerships

Quick Index

Developers

**Alliance Program**

-Start Here-Conduits Creator ID Dev Exchange Dev Nation Go

# Printer-friendly version Detailed article information

How do I programatically add mail to the outbox of the built-in Mail applica

To add mail to the outbox of the built-in mail application, you'll need to populate a MailAddReco information and call SysAppLaunch with the sysAppLaunchCmdAddRecord launch code.

The MailAddRecordParamsType struct definition can be found in AppLaunchCmd.h.

Here is a code example:

```

static void AddToMailApplication()

MailAddRecordParamsPtr theMailInfoPtr;

LocalID theDBID;

UInt theCardNo;

DmSearchStateType theSearchState;

DWord theResult;

// Allocate the new pointer for the "add-mail" paramaters

theMailInfoPtr = MemPtrNew(sizeof(MailAddRecordParamsType));

if (!theMailInfoPtr)

return;

// Setup all the information for our message

theMailInfoPtr->secret = false;

theMailInfoPtr->signature = false;

theMailInfoPtr->confirmRead = false;

theMailInfoPtr->confirmDelivery = false;

theMailInfoPtr->priority = mailPriorityNormal;

theMailInfoPtr->subject = "Subject";

theMailInfoPtr->from = "a@b.com";

theMailInfoPtr->to = "b@b.com";

theMailInfoPtr->cc = "c@b.com";

theMailInfoPtr->bcc = "d@b.com";

theMailInfoPtr->replyTo = "e@b.com";

theMailInfoPtr->body = "Body...";

// Grab the Local ID and card number of the built-in mail application

DmGetNextDatabaseByTypeCreator(true, &theSearchState, sysFileTApplication,

/ Finally, tell the mail application to add this item to the outbox

if (theDBID)

SysAppLaunch(theCardNo, theDBID, 0, sysAppLaunchCmdAddRecord, (Ptr

// Finally, free up the memory we allocated for the mail information.

MemPtrFree( theMailInfoPtr );

```

#### **Article Information**

Article ID: 1213 Article Type: FAQ

# Base = OX FFFF 600 Table 1-3. Programmer's Memory Map

| Address                  | Name                                    | Width | Block   | Description                                                    | Reset Value(hex)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|-----------------------------------------|-------|---------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Base+\$000               | SCR                                     | 8     | SIM     | System Control Register                                        | \$0C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Base+\$100               | GRPBASEA                                | 16    | CS      | Chip Select Group A Base Register                              | \$0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Base+\$102               | GRPBASEB                                | 16    | CS      | Chip Select Group B Base Register                              | \$0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Base+\$104               | GRPBASEC                                | 16    | CS      | Chip Select Group C Base Register                              | \$0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Base+\$106               | GRPBASED                                | 16    | CS      | Chip Select Group D Base Register                              | \$0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Base+\$108               | GRPMASKA                                | 16    | CS      | Chip Select Group A Mask Register                              | \$0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Base+\$10A               | GRPMASKB                                | 16    | CS      | Chip Select Group B Mask Register                              | \$0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |